## CONPOUND SENICONDUCTOR Connecting the Compound Semiconductor Community

Volume 25 Issue 1 JANUARY/FEBRUARY 2019

🈏 @compoundsemi

www.compoundsemiconductor.net

Producing a powerful gallium oxide portfolio

Cranking up production of InP lasers

Giving chips logic and wireless capability

......

Refining SiC growth for high-volume production

Splitting SiC addresses substrate shortages

**Inside** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

## Global mega trends require best performance III-V materials AIX 2800G4-TM

1 and

3D sensing

Augmented reality

Autonomous driving

Cloud computing

Internet of things

Next generation displays

Discover the MOCVD tool of record for AsP-based applications

Made in Germany

www.aixtron.com

# Viewpoint

By Dr Richard Stevenson, Editor

### Making LEDs on metal films

THERE'S A LOT TO BE SAID for directemitting LED displays. Compared to the incumbents – LCDs and OLEDs – they definitely have the upper hand on two key fronts, efficiency and brightness. Those attributes matter a great deal today, as consumers want their devices to last a long time between charges, and have screens that can be read in bright sunlight.

Today's displays do impress, however, when it comes to delivering a high resolution. Take the Apple retina line of products. They have more than 200 pixels per inch, a density that gives the iPad more than 3 million pixels.

It's clear that maintaining this level of resolution with microLEDs will not be easy. The most popular approach involves parallel transfer of LEDs to ensure reasonable production times, but it's going to have to be thousands of chips at a time.

That's not the only headache. Placement must have micronscale precision, and yield must be exceptional – dud pixels are completely unacceptable, and replacing them with ones that work is costly and time-consuming.

Fortunately, this is not the only approach to production. Offering an alternative is iBeam Materials, a spin-out of Los Alamos National Laboratory. It has developed a process for growing LEDs directly on a metal foil via an ion-beam assisted

deposition process, which deposits a single-crystal intermediary layer (see p.18 for details).

On this layer iBeam's engineers add a blueemitting LED layer that can be processed into pixels, comprising three sub-pixels. Red and green sub-pixels are created by adding quantum-dot, down-converting layers – depending on the size of the LEDs, these colour converters can be added as a photoresist matrix, or with an inkjet printer.

To turn the pixels off and on, additional material is deposited and patterned to create an array of transistors above the LEDs.

There are many, many merits to this approach. For starters, the metal foil leads to a display that can bend, flex, and wrap around a curved surface.

What's more, the cost of the technology is very promising. The use of metal foils enables roll-to-roll manufacturing. Use this in conjunction with a deposition process that supersedes MOCVD, and LED costs could fall so far that these displays would be cheaper than those based on OLEDs.

I know you know that there are many pitfalls in converting a promising technology into one that revolutionises an industry. But there is no doubt that iBeam's approach has plenty of potential.

Editor Richard Stevenson richardstevenson@angelbc.com +44 (0)1291 629640 Design & Production Manager Mitch Gaynor +44 (0)1923 690214 mitch.gavnor@angelbc.com Contributing Editor Rebecca Pool +44 (0)1923 690200 editorial@rebeccapool.com Circulation Director Jan Smoothy ian.smoothv@angelbc.com News Editor Christine Evans-Pughe chrise-p@dircon.co.uk Chief Executive Officer Stephen Whitehurst stephen.whitehurst@angelbc.com +44 (0)2476 718970 Sales Executive Jessica Harrison jessica.harrison@angelbc.com +44 (0)2476 718209 Directors Bill Dunlop Uprichard - EC, Stephen Whitehurst - CEO, Jan Smoothy - CFO, USA Representatives Tom Brun Brun Media tbrun@brunmedia.com +001 724 539-2404 Jackie Cannon, Scott Adams, Sharon Cowley, Sukhi Bhadal Janice Jenkins iienkins@brunmedia.com +001724-929-3550Publisher Jackie Cannon Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, jackie.cannon@angelbc.com +44 (0)1923 690205 Director of Logistics Sharon Cowley +44 (0)1923 690200 sharon.cowley@angelbc.com Coventry CV5 6SP, UK, T: +44 (0)2476 718 970 E: info@angelbc.com

On the cover: A blue LED device with probes on the contact pads of the 300 micrometer mesa structure. The atomically smooth epi-GaN/InGaN device layers were grown directly on the rough metal foil (visible here through the GaN layer) by the team from iBeam Materials and Sandia National Labs in New Mexico, USA.

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publication. Angel Business Communications Ltd @ Business Communications Ltd will be happy to part without the writter consent of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coventry CV5 6SP UK. The 2019 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Periodicals postage paid at Jamaica NY 11431. US Postmaster: Send address changes to Compound Semiconductor, Air Business Ltd, c/o Worldnet Shipping Inc., 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Printed by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) @ Copyright 2019.

# CONTENTS

#### 18 COVER STORY Making microLEDs on metal foils

The manufacture of microLED displays can take a big step forward by switching to the monolithic integration of transistors and LEDs grown on metal foils

#### 28 Full steam ahead for CST Global

While Brexit is doing no favours to CST Global, it is certainly not derailing its phenomenal growth, foundry build-out and expansion of its customer base

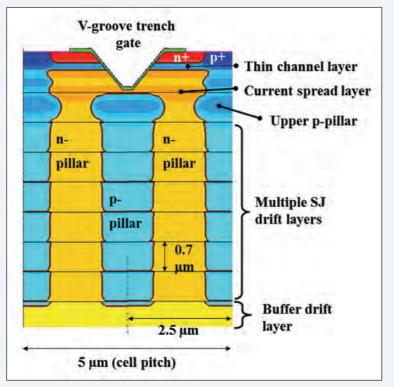

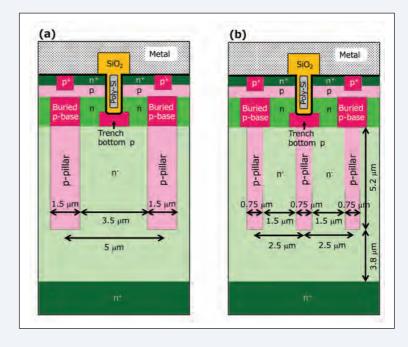

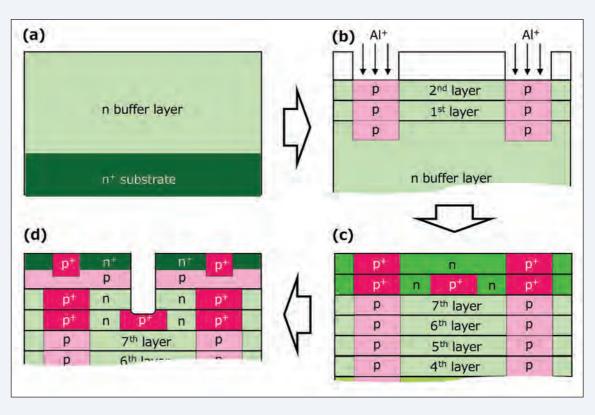

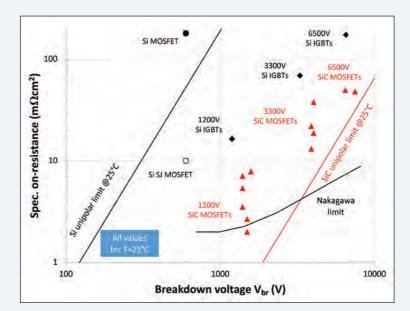

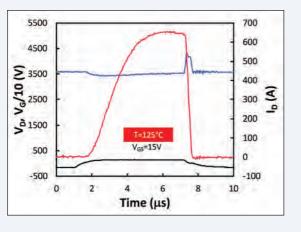

## 38 Showcasing silicon carbide

Super-junctions and sulphur doping take SiC MOSFETs to new highs

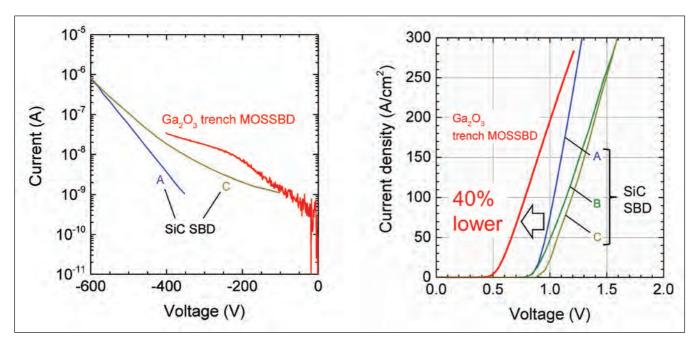

#### 44 Producing a gallium oxide power portfolio

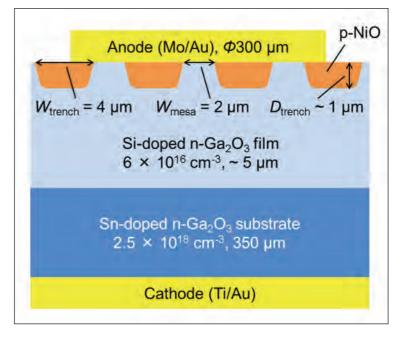

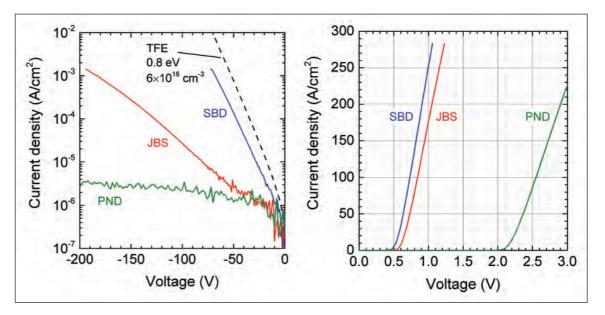

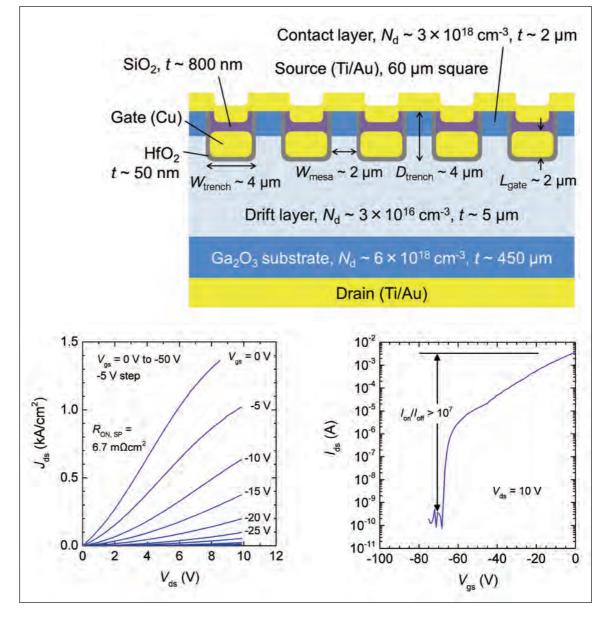

Gallium-oxide trench-type power devices with novel architectures have the attributes to trump those made from silicon carbide

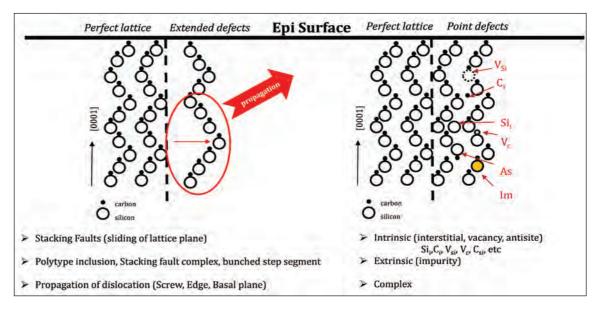

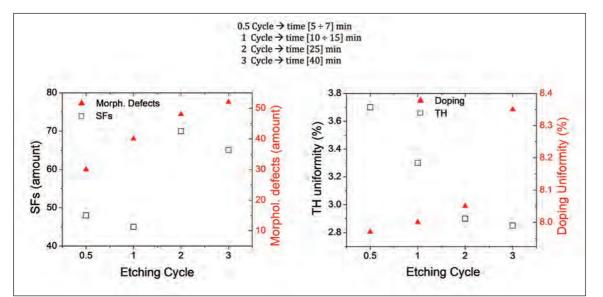

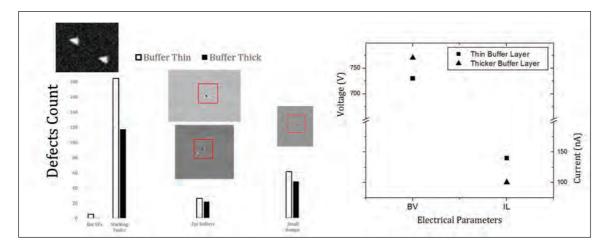

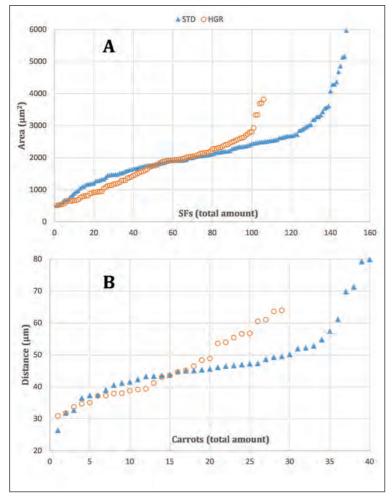

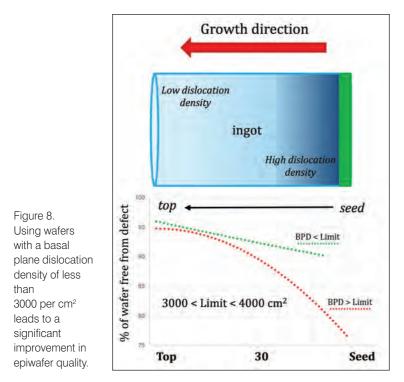

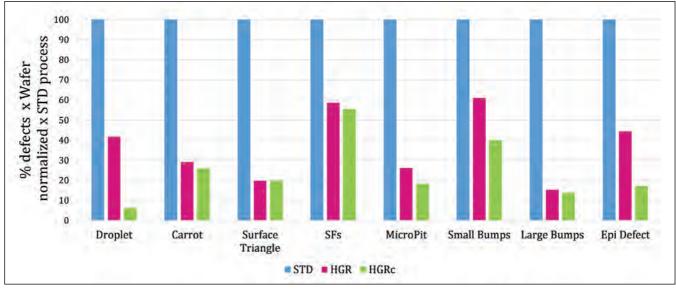

#### 54 Refining SiC epi-growth for high-volume production

Screening the substrate, optimising a fast growth process and going slow in the cool-down step are three ingredients to high-yield, high-volume production of SiC epiwafers

## 60 Combining logic and wireless

Equipping silicon with InGaAs channels improves the logic and high-frequency performance of RF-CMOS

#### news

- 06 EC Unlocks €1.75 billion for compound semiconductor project

- 07 Samsung shows microLED products at CES 2019

- 08 European InP PIC pilot project takes off

- 09 EPC announces AEC qualified EGaN FETs

- 10 Akash wins approval for GaN-on-diamond satellite launch

- Crystal IS UVC LEDs for new EU drinking water rules

#### news analysis

#### 12 Infineon tackles SiC supply shortages

Infineon's acquisition of Siltectra secures SiC wafer supply for the German semiconductor manufacturer

#### 14 Nitride Semi enters Micro-LED display market

Japanese UV-LED manufacturer, Nitride Semiconductor, claims to have developed an easy way to make microLEDs for better performing displays

#### 16 Transphorm readies for rapid GaN growth

With solid reliability data in tow, Transphorm is set to ramp GaN production to meet rising market demand

#### research review

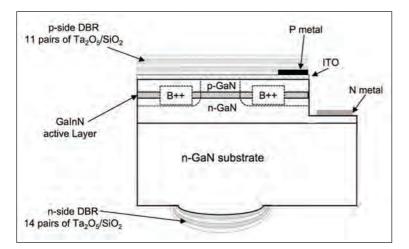

#### 66 Craffing curved mirror VCSELs

GaN VCSELs with long cavities and curved mirrors combine very low threshold currents with high production yields

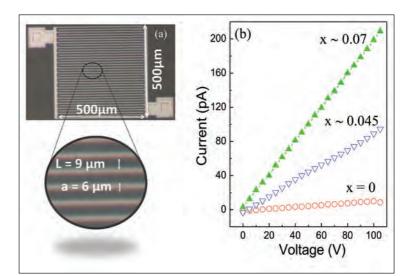

#### 67 Unlocking the promise of layered nitrides

MOCVD-grown hexagonal BGaN heterostructures underscore the potential of this layered, wide bandgap material system

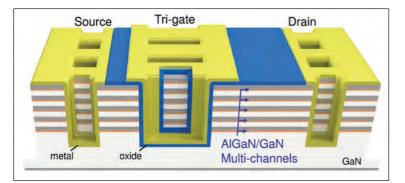

#### 68 GaN HEMTs: Trimming resistance with multiple channels

HEMTs with multiple channels and a tri-gate trim resistance and boost drain current while delivering a high blocking voltage

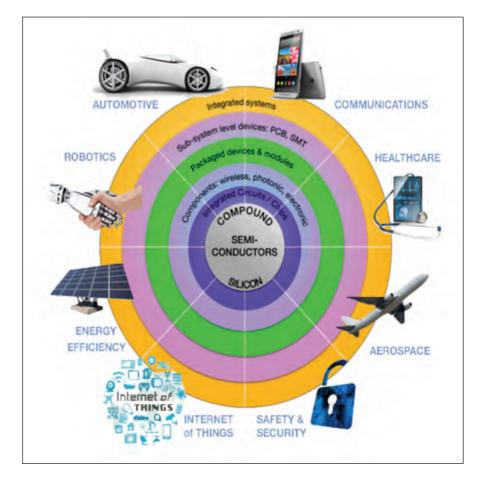

## EC Unlocks €1.75 billion for compound semiconductor project

Welsh Economy Minister, Ken Skates has welcomed the European Commission's approval of an innovative plan, spearheaded by Wales that identifies compound semiconductors as an important sector.

The plan will unlock  $\in 1.75$  billion of funding for research activities, will bring in up to  $\in 6$  billion in private investment and will ultimately help bring new technology innovations to market.

The overall objective of IPCEI is to deliver an integrated and collaborative approach to research and innovation to develop innovative components and technologies for use in applications including 5G communications, connected autonomous vehicles, and other next generation commercial and industrial devices.

It is expected to benefit both the Welsh and the wider UK economy by establishing South East Wales as the leading centre of compound semiconductor expertise.

The UK element of the pan-European joint microelectronics research and innovation project was driven by the Welsh Government and involves three Welsh companies: IQE, Newport Wafer Fab and SPTS Technologies (an Orbotech company), along with Manchester based ICS Ltd.

Economy Minister, Ken Skates said: "Wales' semiconductor cluster and its contribution to many of the technologies that are so prevalent in our modern everyday lives is a real source of pride, and I am delighted Wales has taken the lead on behalf of the UK in co-ordinating this project that will drive vital research and accelerate innovation work across Europe.

"The EU's decision to approve the plan is huge news for the sector and of course for Wales' wider economy, paving the way for up to £6 billion of private investment throughout Europe and enabling our own semiconductor companies to work alongside international giants in their field.

"We look forward to working closely with our European partners and IQE, Newport Wafer Fab and SPTS on this exciting work and will do all we can to deliver the very best outcome for Wales."

Commissioner Mariya Gabriel, in charge of Digital Economy and Society said: "Every connected device, every modern machine, all our digital services depend on microelectronic components that become smaller and faster with time.

If we don't want to depend on others for such essential technology, for example for security or performance reasons, we have to be able to design and produce them ourselves. The decision to approve the project is a result of enhanced cooperation and shared European vision." The UK is already home to a number of state-of-the-art businesses and research facilities in the compound semiconductor space with a particular concentration in Wales. The South Wales semiconductor cluster – branded as CSconnected – is rapidly being recognised as a leading centre for enabling technologies powered by compound semiconductors.

The Commission's approval of the project means that member states can provide up to  $\in$ 1.75 billion of funding for first deployment and innovation. This is expected to open doors to an additional  $\in$ 6 billion in private investment.

The overall objective of IPCEI is to deliver an integrated and collaborative approach to research and innovation to develop innovative components and technologies for use in applications including 5G.

## Samsung shows micro LED products at CES 2019

SAMSUNG ELECTRONICS has introduced the latest innovations in modular MicroLED display technology during its annual CES event at the Aria Resort & Casino in Las Vegas.

The new MicroLED technology designs featured at the event included: a new 75 inch display, a 219 inch The Wall as well as other various ground-breaking sizes, shapes and configurations for a next-generation modular MicroLED display - a 2019 CES Best of Innovation Award winner.

"For decades, Samsung has led the way in next-generation display innovation," said Jonghee Han, president of Visual Display Business at Samsung Electronics. "Our MicroLED technology is at the forefront of the next screen revolution with intelligent, customisable displays that excel in every performance category. Samsung MicroLED has no boundaries, only endless possibilities."

Featuring self-emissive technology and modular capabilities, Samsung's MicroLED displays deliver high picture quality, versatility and design. These TV displays are made up of individual modules of self-emissive MicroLEDs, featuring millions of inorganic red, green and blue microscopic LED chips that emit their own light to produce brilliant colours on screen – delivering unmatched picture quality that surpasses any display technology currently available on the market. At last year's CES, Samsung

introduced MicroLED by unveiling The Wall, the critically acclaimed, awardwinning 146 inch MicroLED display. Due to the technical advancements in the ultra-fine pitch semiconductor packaging process that narrow the gap between the microscopic LED chips, Samsung has been able to create a stunning 4K MicroLED display in a smaller, more home-friendly 75 inch form factor.

Thanks to the modular nature of MicroLED, this technology offers flexibility in screen size that allows users to customise it to fit any room or space. By adding MicroLED modules, users can expand their display to any size they desire. The modular functionality of MicroLED will allow users in the future to create the ultimate display event irregular  $9\times3$ ,  $1\times7$  or  $5\times1$  screen size that suits their spatial, aesthetic and functional needs. Samsung says its MicroLED technology also optimises the content no matter the size and shape of the screen. Even when adding more modules, Samsung MicroLED displays can scale to increase the resolution – all while keeping the pixel density constant. Additionally, MicroLED can support everything from the standard 16:9 content, to 21:9 widescreen films, to unconventional aspect ratios like 32:9, or even 1:1 – without having to make any compromises in its picture quality.

Finally, because MicroLED displays are bezel-free, there are no borders between modules - even when you add more. The result is a seamless, infinity pool effect that allows the display to elegantly blend into any living environment.

#### Advanced Compound Semiconductor Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

#### MasimoSemiconductor.com | 603-595-8900

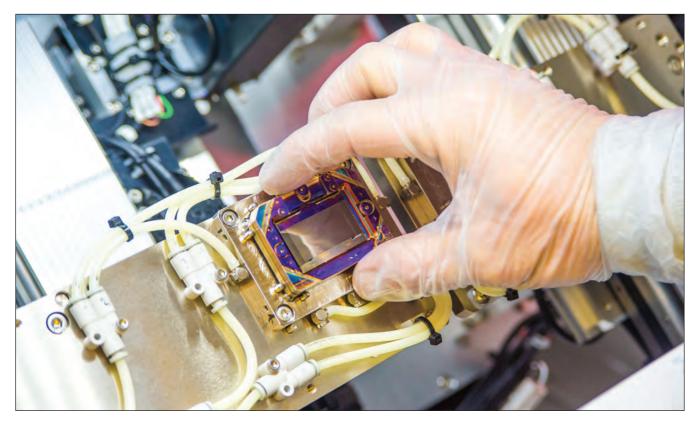

## European InP PIC pilot project takes off

TWELVE partners from northwestern Europe are creating an open access PIC (photonic integrated circuit) pilot line that it is claimed will drastically reduce costs and time for the pilot production of new products. This new facility is projected to be the incubator of a thousand new companies and thousands of jobs. The  $\in$ 14 million project (OIP4NWE) is supported by the European Regional Development Fund.

One of the main hurdles for PIC production is the high cost involved in R&D. Not only does it require expensive high-tech equipment installed in cleanrooms, but currently the production processes still have a high defect rate and are too slow. This was workable for basic research but not for commercial R&D.

The new project, led by photonics stronghold Eindhoven University of Technology (in collaboration with its Photonic Integration Technology Centre), consists of the realisation of an efficient pilot production line for shared use by European SMEs. It should take the defect rate in pilot production down and the throughput time will be shorter. All in all, this should lead to a cost reduction which significantly lowers the threshold for developing new photonic products. This should help establish a thousand integrated photonics firms within ten years after the project.

The front-end process (production of PICs on InP wafers) will be realised in the existing NanoLab at Eindhoven University. The PICs of different companies will be combined on one wafer to keep costs low. The back-end process is done at the Vrije Universiteit Brussel (Optics for beam shaping and light coupling) and at the Irish Tyndall National Institute (Assembly of fibreoptic connections and electronics in the package). All steps require nanoscale precision to avoid product defects.

The first stage of the project is equipment installation. The second stage focusses

on automation of the equipment while a third stage will involve intensive industrial research together with equipment manufacturers to optimise and develop new processes.

The line should be fully in operation in 2022. To incentivise the initial uptake by SMEs, a voucher scheme for external SMEs will be set up. The other parties involved are the companies Aixtron SE (Germany), SMART Photonics, VTEC Lasers & Sensors, Technobis Fibre Technologies (all Netherlands), mBryonics Limited (Ireland) and Oxford Instruments nanotechnology Tools (United Kingdom) along with research centres Photonics Bretagne (France), Cluster NanoMikroWerkstoffePhotonik.NRW (Germany) and Photon Delta Cooperatie (Netherlands).

The project has a total budget of  $\in$ 13.9 million. Of this, the EU is funding  $\in$ 8.3 million, with the remainder coming from the participating parties.

#### Osram and GaN systems develop LiDAR driver

OSRAM Opto Semiconductors has announced an ultrafast laser driver with a high-power, multi-channel Surface Mount (SMT) laser for LiDAR (Light Detection And Ranging) systems. It has worked with GaN Systems to develop the technology.

One of the issues with LiDAR technology has been its inability to transmit lasers at short pulses, while maintaining high peak power, which is necessary to ensure that the LiDAR is eye safe with a long range and high resolution. To address this need, Osram worked with GaN Systems to develop a laser driver with a one nanosecond pulse rise time, while driving all four channels at 40 A each to deliver 480 W peak power.

This peak power then can be modulated at low-duty cycles to produce high resolution 3D cloud points at long range for new LiDAR designs. "Operating at the elevated current levels and nanosecond rise times necessary for long-distance LiDAR requires the high power, high frequency and robust thermal performance that are the hallmarks of GaN Systems' products," said Jim Witham, CEO of GaN Systems. "It is great to see the industry recognise these performance attributes and leverage them for its systems."

Scanning LiDAR is a key technology for Advanced Driver-Assistance Systems (ADAS), which is designed to increase road safety and enable autonomous driving. These electronic devices react instantly to potential collisions without wasting precious seconds of reaction time. Scanning LiDAR creates high-resolution 3D images of a car's surroundings and registers obstacles early enough for ADAS or self-driving cars to initiate the appropriate driving manoeuvres, such as automatic braking to prevent collisions.

"Osram enables LiDAR technology for autonomous vehicles by not only developing high power, multi-channel SMT lasers that meet automotive quality standards, but also working with ecosystem partners like GaN Systems to address the technological barriers that arise", said Rajeev Thakur, senior marketing manager at Osram Opto Semiconductors. "Our lasers are leading the way to make autonomous driving a reality for everyone."

Osram has continuously expanded its laser portfolio for LiDAR to accommodate the needs of customers, including increasing the peak power of the SPL DS90A\_3 to 120 W at 40 A. In addition, Osram plans to release a four-channel SMT laser in 2019. The additional channels increase the field of view and total peak power, with each channel being capable of generating 120 W.

news review

## **EPC** announces **AEC** qualified EGaN FETs

EPC has announced the successful AEC Q101 qualification of two additional eGaN devices, addressing a range of applications in the automotive industry and other harsh environments. The new products, EPC2206, and EPC2212 are both discrete transistors in wafer level chipscale packaging (WLCS) with 80  $V_{DS}$  and 100  $V_{DS}$  ratings respectively.

eGaN technology has been in mass production for over eight years, accumulating billions of hours of successful field experience in automotive applications, such as LIDAR (Light Detection and Ranging) and radar for autonomous cars, 48 V - 12 V DC-DC converters used in data centre computers, ultra-high-fidelity infotainment systems, and high-intensity headlamps for trucks. These new devices have completed rigorous automotive AEC Q101 qualification testing and will be followed with several more discrete transistors and integrated circuits designed for the harsh automotive environment.

Lidar High Fidelity Infotainment Market A& V Power Distribution Radar LED Headlamps

current rating of 390 A in a 6.1 mm x 2.3 mm chip-scale package. The EPC2212 is a 100 V, 13.5 m $\Omega$  component with a pulsed current rating of 75 A in a 2.1 mm x 1.6 mm chip-scale package. These eGaN FETs are many times smaller and achieve switching speeds 10 - 100 times faster than their silicon MOSFET counterparts.

The EPC2206 device is suited for vehicles using 48 V bus power distribution to manage the power-hungry electronicallydriven functions and features appearing on the latest cars. Electric start-stop, electric steering, electronic suspension, and variable speed air conditioning are a few examples. And now, with the emergence of self-driving vehicles, additional demands from systems such as LIDAR, radar, camera, and ultrasonic sensors are placed upon the power distribution system accelerating the need for automobiles to move to a 48 V bus system. For 48 V bus systems, GaN devices like the EPC2206 increase efficiency, shrink size and weight and reduce system cost.

The EPC2212 is designed for firing the lasers in LIDAR systems because the FET can be triggered to create highcurrent with extremely short

pulse widths. The short pulse width leads to higher resolution, and the higher pulse current allows the LIDAR system to discern objects at greater distances. These two characteristics, along with their tiny size and low cost, make eGaN FETs ideal for radar and ultrasonic sensors in addition to LIDAR in demanding automotive applications.

EPC's CEO and co-founder Alex Lidow notes: "These two automotive products are the next in what will be a constant stream of transistors and integrated circuits designed to enable autonomous driving and improve fuel economy and safety. Our eGaN technology is faster, smaller, more efficient, lower cost, and more reliable than the ageing silicon power MOSFET used in today's vehicles."

#### Innovate UK project delivers 150 mm VCSEL capability

The Compound Semiconductor Centre (CSC), IQE's joint venture with Cardiff University, and its partners (SPTS Technologies, Cardiff University and Swansea University) have announced the successful conclusion of an Innovate UK funded project – 'High Efficiency Manufacturing of Vertical Cavity Surface Emitting Lasers (VCSELs)'.

The EPC2206 is an 80 V, 2.2 m $\Omega$

enhancement-mode FET with a pulsed

The project has delivered key process modules required to transition small diameter manufacturing processes currently used for VCSELs to a high uniformity 150 mm epitaxial platform. The need for scale-up is driven by significant benefits in terms of productivity "(four times more die sites in transitioning from 75 mm to 150 mm ) and yield (driven by smaller ratio of edge sites to total area for larger wafer diameters) to facilitate a step change in cost reduction for VCSELs, and thus accelerate adoption in mass market applications such as 3D imaging, proximity sensing, range-finding and LIDAR.

The work included the commissioning of a custom 150 mm oxidation tool at Cardiff University's Institute for Compound Semiconductors which is used for a particularly challenging stage of preferential oxidation of aluminium rich layers in the VCSEL layer structure, to produce a high efficiency optical waveguide in the device. High quality mesa dry etch processes to  $>5\mu$ m were developed by SPTS on GaAs/AlGaAs epitaxial structures supplied by CSC, with Swansea supporting PECVD and photo process steps, to complement the oxidation process module; essential for a high uniformity, high reliability 150 mm VCSEL fabrication platform. A robust process solution was developed, including in-situ depth targeting end-point detection capability. A benchmark of  $<\pm5\%$  mesa depth uniformity across a full 150 mm VCSEL epitaxial wafer structure was demonstrated.

The capability will form the core of a future 150 mm VCSEL prototyping capability which will be leveraged by the consortium to work on custom VCSEL development, device-scale optimisation and validation of VCSEL epitaxial materials development as a core research and manufacturing competence in the emerging CSconnected Compound Semiconductor Cluster in South Wales.

## Akash wins approval for GaN-on-diamond satellite launch

AKASH SYSTEMS, a company focused on next generation mini satellites, has been granted an Experimental Special Temporary Authority (STA) license from the US Federal Communications Commission (FCC) for a satellite launch featuring its proprietary GaN-on-Dimond transmitter technology. The GaN-on-Dimond technology will be integrated into a K<sub>a</sub>-band (17.2 to 20.2 GHz) 3U radio transmitter and launched in a 12U CubeSat allowing for new levels of data transmission for customers to increase capacity and reduce end-user costs.

"Taking the lead in the satellite communications industry, this demo will showcase the use of our proprietary GaN-on-Dimond Radio Frequency (RF) amplifier technology," said Co-founder, CEO and GaN-on-Dimond Inventor Felix Ejeckam. "Beyond the capability to handle the increasing demands of today's extreme data throughput, we are confident future adoption of the system will drive down end-user costs to levels never before seen."

The company's satellite launch will demonstrate the transmitter's capability to handle more than 5 Gbps downlink speeds from a 10 W 3U radio transmitter. Tentatively slated for early 2020, the launch will validate the data rates, reliability and space-qualification readiness of the GaN-on-Dimond

transmitter technology. The new technology enables a smaller, lighter and higher performing satellite that will pave the way to lower launch costs, reduced cost-per-bit, more launch cycles, and increased communications access around the earth.

"Anyone buying our solid-state power amplifiers (SSPAs) to transmit data to or from space will be interested in the space worthiness and reliability of our SSPA products," said Jeanette Quinlan, director of space systems, Akash Systems. "This launch helps us capture that worthiness and reliability data for them."

Akash will continue to focus on scaling up and qualifying its GaN-on-Dimond Power Amplifier product line, offering customers products with higher frequencies that will be announced in the months ahead. The picture above is an artist's rendering of Akash Systems' McNair 12U CubeSat.

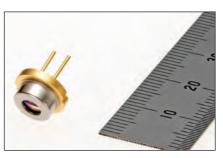

#### Mitsubishi to shrink projectors with new laser diode

MITSUBISHI ELECTRIC has announced the ML562G86 pulse laser diode for projectors, featuring a vibrant 638 nm red light, world-record output power of 3.0 W under pulse operation and mean time to failure (MTTF) of over 20,000 hours.

The ML562G86's high output power and wide operating temperature range will contribute to enhanced projector luminance and miniaturisation. Sample sales began on January 11, 2019 and volume shipping will begin in April 2019. Projector light sources are shifting from mercury lamps to solid-state light sources that offer wall-plug efficiency, a wide colour gamut, and highly reliable operation. LDs achieve the best wall-plug efficiency among solid-state light sources, thereby contributing to lower power consumption, and thus are viewed as the most promising new light source for projectors. Mitsubishi Electric expects to use laser diodes to develop not only superior projectors but also advanced laser TVs capable of more vibrant images than liquid-crystal TVs.

In September 2015, Mitsubishi Electric released its ML562G84 high-power red laser diode, which achieved 2.5W output under pulse operation as a red laser diode in three RGB light sources for projectors. With conventional laser diodes, extended operation at 3.0 W output power causes the laser's light-emitting surface crystals to

melt, making it difficult to achieve an MTTF of 20,000 hours. In response, Mitsubishi Electric has developed the technology required to suppress degradation of the light-emitting surface even at 3.0 W, leading to the newly announced ML562G86 red laser diode that achieves unprecedented 3.0 W output power.

### Crystal IS UVC LEDs for new EU drinking water rules

AN OCTOBER 2018 vote on proposed water guidelines in Europe ruled in favour of more stringent quality standards for consumer drinking water, expanding monitoring and limits on certain pollutants, including legionella. Now Crystal IS, a developer of highperformance UVC LEDs, has announced independent testing results of the Klaran AKR, an on-demand UVC LED-based water disinfection reactor designed by Asahi Kasei Corporation, the parent company of Crystal IS, intended for consumer and commercial water purification. Performed by the University of Colorado Boulder, testing showed the AKR reactor provided 99.998 percent reduction of legionella pneumophila at a flow rate of two litres per minute.

The recently passed Revision of the Drinking Water Directive in the European Union notes that legionella causes the highest health burden of all waterborne pathogens in the Union and proposes to apply random monitoring at the tap to man-made water systems and subsequent remediation actions to improve water safety. The performance of the Klaran AKR would provide an immediate risk management solution for meeting the <1000 CFUs/Litre assessment value. "UVC LED technology enables water product manufacturers to differentiate their solution with point-ofdispense disinfection, supporting new and existing customers in mitigating the risk of legionella," said James Peterson, product manager, Crystal IS. "The Klaran Reactor series uses our UVC LEDs to provide maintenance-free disinfection that lasts longer and is more affordable than UV lamps or filtration cartridges. Along with its compact size, this makes the Klaran AKR an ideal method of worryfree legionella management."

Enforcing regular monitoring at the point of dispense would not only improve water hygiene from large and small utility systems, but also promote new risk identification mechanisms inside of building distribution systems and water holding appliances. In addition to potentially improving public health, raising consumer confidence and reducing cases of Legionnaires' Disease, this regulation would place increased accountability for water hygiene on building managers and water product designers in the European Union. While individual Member States, system operators, and building managers will need to interpret their risk reduction plans based upon the final legislation, water purification and appliance manufacturers

are acting on these future needs now to provide new solutions for this existing health concern and upcoming regulatory situation. Lasting for years after installation rather than months, Klaran reactors provide effective water hygiene without maintenance schedules or burdens to owners and service providers. As both facilities and product designers face the task of identifying low impact strategies to improve legionella management, Klaran UVC LED-based reactors will offer long term and unobtrusive installation into water systems, while providing reliable performance claims backed by third party validation. Klaran AKR reactors are available for design integration sampling now.

#### PlayNitride picks Aixtron for micro LED production

Aixtron, a provider of deposition equipment, has announced that the Taiwanese MicroLED firm PlayNitride, will receive an AIX G5+ C MOCVD system for the manufacturing of GaN-based MicroLEDs. They companies have also signed a joint collaboration agreement to technically and commercially work together.

MicroLED technology is a major challenger to existing display technology for next-gen consumer products. Displays made of MicroLEDs consist of micron-sized LED arrays forming individual sub-pixel elements. Compared to the existing LCD and OLED technologies, MicroLED displays offer lowest power consumption while exhibiting superior pixel density, contrast ratio and brightness. Thus, opening new horizons for consumer mobile products as well as premium TV displays. PlayNitride has chosen the AIX G5+ C for MicroLED MOCVD processing. Aixtron's advanced production tool is said to offer market leading wavelength uniformity to meet the tightened MicroLED market specifications in a batch reactor highthroughput environment. Furthermore, the system is designed to allow for very low defect and particle levels due to an effective *in-situ* cleaning technology and the cassette-to-cassette handler which is essential for high yields.

"We are very pleased that PlayNitride as a key player in the business has selected the AIX G5+ C for the further development of ground-breaking MicroLED production processes. We are looking forward to our joint collaboration to accelerate a breakthrough in the commercial and technical use of MicroLEDs for displays. Our AIX G5+ C platform perfectly backs PlayNitride's product strategy since it allows for outstanding performance in a highvolume manufacturing environment", comments Bernd Schulte, president of Aixtron. Taiwan-based PlayNitride was established in June 2014 to research and develop nitride-related materials and applications. The company is now focusing on GaN-based MicroLEDs – it is branding its technology as PixeLED displays and has recently demonstrated MicroLED display prototypes.

In April 2018 Taiwan's Ministry of Science and Technology approved PlayNitride's application to setup a \$17 million production facility at Hsinchu Science Park. PlayNitride aims to produce MicroLEDs, display modules and panels at its new facility at Hsinchu. news analysis

## Infineon tackles **SiC supply** shortages

Will Infineon's acquisition of Siltectra secure SiC wafer supply for the German semiconductor manufacturer, asks **Rebecca Pool.**

IN A BID to guarantee materials supply, Infineon bought Dresden-based start-up, Siltectra, for  $\in$ 124 million, last month.

At a time when shortages in SiC wafer supplies rumble on, Siltectra has developed a novel technology – 'cold splitting' – to process crystals with minimal materials loss.

The technology is used to split SiC wafers and double the number of chips produced from one wafer. Importantly, Infineon now hopes to industrialise this process.

As Peter Friedrichs, Infineon's senior director of wide band gap semiconductors, puts it; "A huge motivation for this acquisition is security of supply and production ramp capability."

"Given the silicon carbide shortage of supply, especially with 150 mm wafers, we just want to make sure that if this continues, we are able to still deliver to customers," he adds.

Founded in 2010, Siltectra has spent the last eight years developing its wafer-splitting process and building a solid patent base. The spalling process uses externally applied stresses to separate crystalline materials along crystal planes with a well-defined thickness.

A laser defines a layer within the crystal to a predefined depth, with a custom polymer foil then deposited onto the top of the material. This materials system is then rapidly quenched to around -160  $^{\circ}$ C to induce enough stress to mechanically split the

material along its laser-defined layer, separating a wafer from the rest of the boule. The polymer foil can then be removed from the new wafer by standard wetchemical cleaning. And, importantly, the remaining crystal boule can then be prepared for the next 'bonus' wafer, vastly reducing manufacturing costs.

Materials gains aside, cold-splitting promises other benefits. As Friedrichs highlights, the mechanical stresses from traditional wire-saw processes far outweigh those imposed by cold-splitting, so the new process yields wafers with fewer defects.

What's more, the process can also be used on GaN, GaAs and sapphire wafers, although Infineon intends to focus on SiC in the next few years.

But crucially, results to date indicate that the process can thin wafer materials to 100  $\mu$ m and below in minutes with high precision and virtually no material loss, a feat that Infineon now intends to repeat at production scale.

"Right now, we have a proof-of-concept, laboratory scale process, so we now need to scale up and

automate the process to run with high throughput, twenty four hours a day, seven days a week," says Friedrichs. "As part of this, we need to define the equipment for a mass manufacturing process from scratch, as there is nothing else that is out there."

"You know, the company in Dresden is a start-up, has used demonstrator tools and sometimes even home-made equipment," he adds. "The challenge for us is that there is nowhere to order new equipment for scale, so we are now partnering with companies that can manufacture the necessary production equipment that can be implemented into an automated manufacturing set-up."

All in all, the company estimates that the transfer to volume production will be completed within the next five years. Industrialisation is set to take place at Siltectra's existing Dresden site as well as Infineon's SiC manufacturing site and headquarters in Villach, Austria.

According to Friedrichs, final SiC chip production will take place at Villach, and Infineon will not create an additional manufacturing site at Dresden. "As an intermediate situation, we might also use Dresden for some initial pre-production trials," he says. "But the plan is to use the Dresden facility for alternative development in other directions."

#### Proving the process

Earlier this year, Siltectra revealed it had produced GaN-on-SiC HEMT devices on split-off wafers, with Friedrichs confirming Infineon has also fabricated practical devices. And with question marks still hanging over the supply of SiC wafers – only a few months ago industry analyst firm Yole Développement confirmed the supply bottleneck remained – Infineon's latest acquisition looks set to ease the ramp-up of SiC devices.

"The biggest motivation for this has been to increase the availability of SiC material," emphasises Friedrichs. "With cold-splitting we can simply double the number of wafers that we have allocated to our long-term agreements with suppliers."

"This is our first counter-measure to tackle the materials shortage problem and is part of our long-term strategy to roll out technologies relating to silicon carbide," he adds.

#### news analysis

## Nitride semiconductor enters micro-LED display market

Japanese UV-LED manufacturer, Nitride Semiconductor, claims to have developed an easy way to make micro-LEDs for better performing displays. **Rebecca Pool** finds out more.

> LAST NOVEMBER, Japan-based UV LED manufacturer, Nitride Semiconductors, set-up a 100 percent owned subsidiary, Micro Nitride, to develop and manufacture micro UV-LED chips for micro-LED displays.

Initially targeting flexible displays for next-generation smartphones, Nitride Semiconductors is ploughing 100 million yen – nearly £700,000 – into its new venture and expects displays to reach commercial markets come 2020.

"LED prices are coming down and down, and Chinese companies are getting bigger and bigger," says Nitride Semiconductors president and chief executive, Yoshihiko Muramoto. "Japanese LED makers are now in a difficult situation and need to add value, we need to make displays and not just LEDs, so we have established our new company." Nitride Semiconductors unveiled its first UV LED in 2000 and has since delivered myriad wafers, chips and modules to UV LED markets worldwide. Its new subsidiary will now produce micro UV-LED chips that comprise the micro UV-LED and a red, green, blue (RGB) phosphor to generate 'natural' white light.

Importantly, Muramoto reckons this UV-LED and RGB phosphor approach eases chip manufacture and leads to better-performing displays than existing methods. Today's fledgling micro-LED displays have typically been manufactured with red, blue and green LEDs or a blue LED that excites red and green phosphors.

However, many issues have stymied development. Take the RGB microLED array; mounting different semiconductor structures at high density isn't easy. What's more, current, voltage and response speeds vary from LED to LED, complicating chip control.

#### news analysis

And with the technology in tow, the chief executive says his company's micro UV-LEDs are ready for mass manufacture, claiming fabrication is 'not so difficult'. Importantly, his company is also working with Japan-based display supplier, V Technology, on display manufacture.

#### Pick and place pains

MicroLED displays have been notoriously difficult to manufacture, using traditional pick and place transfer processes in which each sub-pixel is placed onto a CMOS backplane one at a time.

Given this, many companies have been working on mass transfer manufacturing processes, including V Technology. In such a process, thousands of sub-pixels are simultaneously moved from a sapphire or silicon donor carrier to the display substrate. While Muramoto will not disclose details of V Technology's mass transfer process, he emphasises: "[The company] can manufacture these displays relatively easily and they will be ready for market in two years."

In the meantime, the chief executive is confident that come mass production, final display costs will appeal. "We are going to need huge volumes of UV LED chips... but with our micro UV-LED method, we can simplify the structure of the display and the mass transfer process will be relatively easy."

Importantly, Nitride Semiconductors is also in close contact with smartphone manufacturers, which is where Muramoto is certain the micro-LED display action first lies.

He reckons the final cost of a display panel for a smartphone will be around \$50. In contrast, he claims the cost of a similar panel, made using other methods, will be as high as \$400.

"The merit of the micro-LED display is that it is flexible," he says. "So microdisplays should be used for wearable applications and we are talking with smartphone manufacturers about this [for nextgeneration devices]."

"Our technology is not so complicated and has been very easy to realise," he adds. "Our competitors have been struggling, but we can get good results."

Meanwhile, for the micro blue LED excitation method, only the blue light is directly emitted while the red and green light result from phosphor conversion with an associated time lag.

"Synchronising the colour response can be very complicated and we just don't have to manage any time lag," says Muramoto.

"Our micro UV LEDs are also easy to mount and we have a fifty year history of using phosphor; it is very natural for us to use UV LEDs for displays and lighting."

The new subsidiary will focus on technology development, rather than manufacturing. As Muramoto puts it: "Japanese companies should aim to develop strong technologies and patents... there are many big LED manufacturers around the world and we can outsource our technology to them."

## **Transphorm** readies for rapid GaN growth

With solid reliability data in tow, Transphorm is set to ramp GaN production to meet rising market demand.

> TO MARK the end of 2018, Transphorm revealed that it had shipped more than 250,000 high-voltage GaN FETs, which co-founder and chief operating officer, Primit Parikh, believes is testament to rapidly accelerating GaN market adoption.

As he tells *Compound Semiconductor*: "2018 has been a game-changing year for high voltage GaN and we finally believe that the last several years of effort that have gone into GaN are now materialising very quickly."

"Our 650 V GaN FETs are deployed in customers' mass production, high-performance power converters," he adds. "We're already in data centre and industrial sectors, and expect more market penetration in areas such as consumer adapters, as well as volume ramping in these markets."

Transphorm 650V GaN FETs are deployed in a range of customers' mass production power converters.

Crucially for Transphorm, recently available field failure data indicates that products are reliable. According to Parikh, his company's GaN FETs now have more than 1.3 billion field hours of operation with low 'failure in time' rates.

"This is very exciting and it's the first time Transphorm, or any supplier, has comprehensive field failure data," says Parikh. "These statistics only become meaningful at more than a billion hours, so this is a significant milestone for us and also increases customer confidence in GaN."

Without a doubt, solid reliability data can only drive Transphorm's GaN devices further into more applications. Key customers include US-based power supply manufacturer, Bel Power Solutions, Japanbased servo motor manufacturer, Yaskawa Electric, computer peripherals supplier, Corsair, US, Taiwanbased computer power supply maker, Seasonic Electronics and solar/electric power generator developer, Inergy, from the US.

According to Parikh, data centres will continue to be a key market for Transphorm, given the rise in edge computing and hyperscale data centres.

And the company will also target adapters for consumer supplies.

"There is a huge push to increase power density for power levels ranging from 65 W to 150 W within existing form factors, which silicon cannot achieve. GaN can do this," he says.

The chief operating officer also has high hopes for automotive markets. Last year, Transphorm delivered the world's first AEC-Q101 qualified GaN transistor, which at 650 V targeted AC-DC conversion for electric vehicle on-board chargers as well as auxiliary high voltage DC-DC conversion in air conditioning, heating power, steering and oil pumps.

"This paradigm shift to electric vehicles has been so large and from when we first started sampling, customers have really been pulling us in," say Parikh.

Parikh won't be drawn on specific customers but also highlights strong demand from Japan-based automotive manufacturers that want to fit higher power DC-AC power inverters into vehicles.

#### news analysis

"The Lexus, for example, has a 400 W AC power plug but now people want more power with 1.5 kW becoming the norm in brand new vehicles," he says. "GaN can provide the size, weight and thermal performance that is so important here."

Parikh is also certain that Transphorm's stake in the Fujitsu-owned wafer foundry at Aizu, Japan, had been instrumental to fuelling demand there.

"The Fujitsu factory has given us a strong Japanese market presence," he points out. "It has a good reputation as a long standing supplier of silicon products to the automotive sector, has proven GaN production, and has the ability to scale to volumes; this has all helped a lot in these automotive markets."

And in the longer-term, Parikh also hopes to target the mighty drivetrain inverter in electric and hybrid vehicles. "This is a more conservative application but GaN can certainly address its needs," he says.

#### Scaling manufacture

Rising demand dictates rising volumes, and Transphorm is set to scale. Recently claiming that device volumes can be 'easily' increased by a factor of five, Parikh also asserts that the transition from 6-inch to 8-inch wafer production will not be difficult when the market demands it.

"Our ability to scale is strongly linked to the fact that we are a vertically integrated business," says Parikh. "In addition to MOCVD, our Aizu wafer foundry is also a silicon-based foundry, set up for huge volumes of silicon so there is lot of equipment here; we can scale when the need comes as the necessary infrastructure is already in place."

Parikh is also confident that the industry supply chain is now in place, which he claims, may actually place GaN in a better position than rival technology SiC.

"We start with silicon substrates and GaN can run in any existing silicon fab, with the necessary expertise in place," he says. "But look at the overall supply chain for silicon carbide; we see a few companies [including Wolfspeed, Infineon and Rohm] making the silicon carbide substrate, but we are also seeing shortages here, and this is limiting the supply chain."

According to Parikh, in key applications the performance of 650 V GaN devices already surpasses that of SiC, at a lower price point. "So now our goal is to provide GaN devices with better performance than SiC but approaching silicon-like prices," he adds.

Transphorm's volume production plans also come at a time when Infineon has just unveiled its first GaN products, 600 V HEMTs with drivers, for adapter, wireless charging and server applications.

The launch makes Infineon the only company, right now, to offer all power electronics technologies – silicon, SiC and GaN – and, like Transphorm, the Germany-based semiconductor manufacturer is ready for volume production.

Parikh isn't fazed. As he puts it: "More and more companies are either joining the market or have announced ambitions to do this, and companies such as Infineon and Nexperia joining us is great news for GaN as it boosts customer confidence."

"Just as we saw with GaN LEDs, more companies are joining the marketplace and a core set of strong companies, with the strong technologies and IP, will now dominate the market for a few years," he adds. "This includes us, and the ride is just about to begin."

"Infineon and Nexperia joining [the market] is great news for GaN as it boosts customer confidence."

Transphorm Co-founder and Chief Operating Officer, Primit Parikh

## Making microLEDs on metal foils

The manufacture of microLED displays can take a big step forward by switching to the monolithic integration of transistors and LEDs grown on metal foils

BY VLADIMIR MATIAS AND JULIAN OSINSKI FROM IBEAM MATERIALS

EVERY YEAR, billions and billions of LEDs are made by growing epitaxial layers of GaN and its related alloys on sapphire and silicon substrates. But that's not the only option. At iBeam Materials of Santa Fe, NM, we have recently demonstrated that high-quality epitaxial GaN can also be deposited on polycrystalline flexible metal foils. Our technology opens the door to large area, lower-cost production of GaN-based devices with a process that is amenable to roll-to-roll manufacturing.

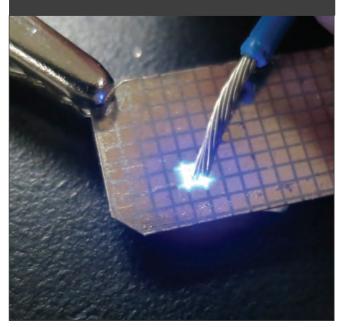

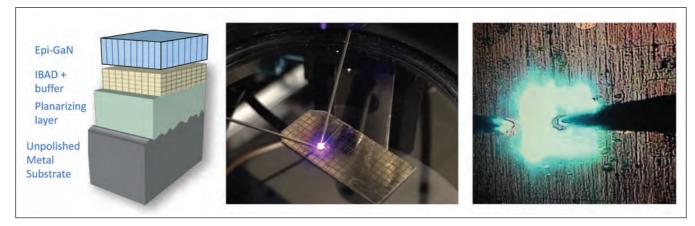

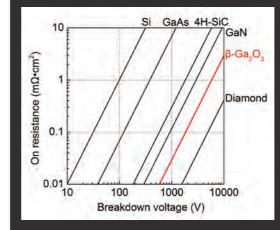

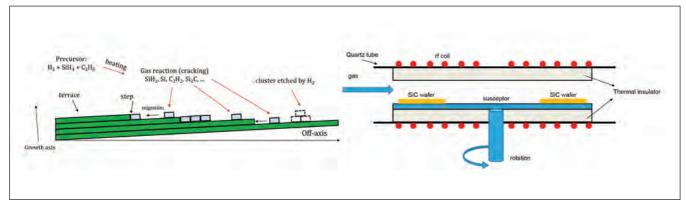

The approach that we employ involves ion-beamassisted deposition. It is used to deposit a singlecrystal-like intermediary layer, which forms the foundation for subsequent epitaxy of nitride layers. Working in partnership with researchers at Sandia National Laboratories and the University of New Mexico, we have used this technology to demonstrate practical LEDs through a project funded by the US Department of Energy, APRA-E (see Figure 1). One of the more attractive opportunities for our ground-breaking technology is in microLED displays, which require large areas of low-cost LED arrays. The most common approach to making these arrays is based on singulation and mechanical transfer. However, there is a move to ever smaller LEDs, making this technique more challenging to implement. It is far better to adopt a monolithic integration approach, which is compatible with our technology.

The microLED market is expected to be huge as it takes market share from LCDs and OLEDs due to the significant advantages that this class of display has over the incumbents. MicroLEDs are brighter and much more efficient, so displays can be read in direct sunlight, and products using batteries will last longer between charges. What's more, these products will provide a longer display lifetime, given the tremendous reliability, lifetime and robustness of the inorganic LED.

Figure 1. iBeam Materials' GaN-on-metal technology relies on a single-crystal-like layer that is created on top of a polycrystalline substrate, such as a long-length metal foil. The single-crystal-like layer is formed by an ion-beam-assisted deposition process. On the left is shown the layer architecture, while photographs show the first LED devices.

Thanks to all these strengths, microLED-based displays should rapidly replace OLED and LCD screens in wearables, cell phones and augmented reality. But this is only the start: LEDs are destined to go on and have success in larger displays as well.

#### Making displays

With the conventional approach to making large-area microLED-based displays, there is a need to use a high-yield process that provides massively parallel transfer of individual LED chips that may be less than ten microns in size. High-definition displays contain 1080 by 1920 pixels, so they require 6.2 million red-green-blue subpixels. And in a 4K display, there are nearly 25 million subpixels. These numbers are so high that in order to minimize the number of transfer steps, LEDs have to be transferred in many thousands at a time.

Several companies are developing technologies for handling in parallel such large groups of LEDs, which could have dimensions down to just 3  $\mu$ m. These approaches have to transfer chips with micron-scale precision, bond them reliably, and realise an incredibly high yield. Even 99.99 percent will not be good enough, as the display could still contain thousands of dead subpixels. They would have to be repaired, because the market will not tolerate even a single malfunctioning or missing pixel in a new device.

Repairing individual pixels is an option, but costs escalate, as this requires additional transfer steps. So it may be better to resort to redundancy in transferring. However, this adds significantly to the LED cost, and it fails to address the problem head-on.

In contrast, we tackle this issue with a technology that can make a paper-thin flexible product with a resolution of 500 pixels per inch or more, and satisfy the market's tremendous desire for integration of displays into thin, curved devices. Using patented GaN-on-metal technology, we grow LED-quality InGaN material directly onto low-cost, large-area flexible metal foil, making monolithic integration of microLEDs practical.

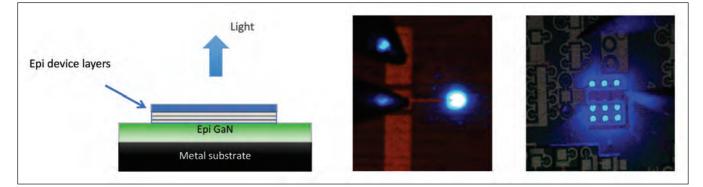

This foil allows our displays to be as good as or better at conforming to curved surfaces than OLEDs. In addition, they may even be able to flex when in use. The conformable metal substrate also provides reflectivity and heatsinking for the LEDs (see Figure 2).

Figure 2. Diagram of an LED cross section, and emission from a 20  $\mu$ m blue LED on metal and an array of microLEDs

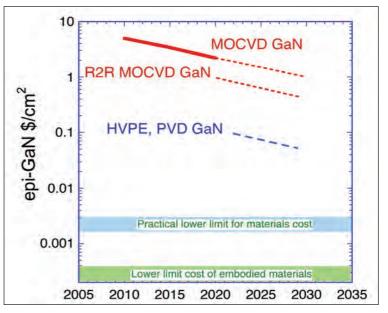

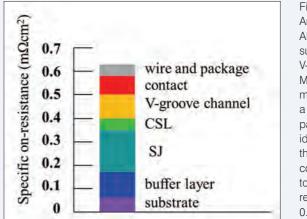

Our technology is compatible with a roll-to-roll process, which, alongside new epitaxial methods that will supersede MOCVD, will slash the cost of manufacturing microLEDs. Currently, costs for MOCVD wafer production are in the range of \$2-3/cm<sup>2</sup>, but they could fall by a factor of three by switching to long-length metal substrate. Further savings will result from the introduction of non-MOCVD deposition processes – our cost model estimates an epi-material cost reduction of more than a factor of ten per unit area (see Figure 3).

Ultimately, LED costs could fall to less than 10 cents per cm<sup>2</sup>. Such a dramatic reduction could allow microLED displays to be even cheaper than those based on OLEDs.

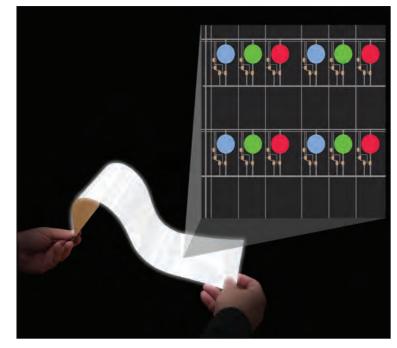

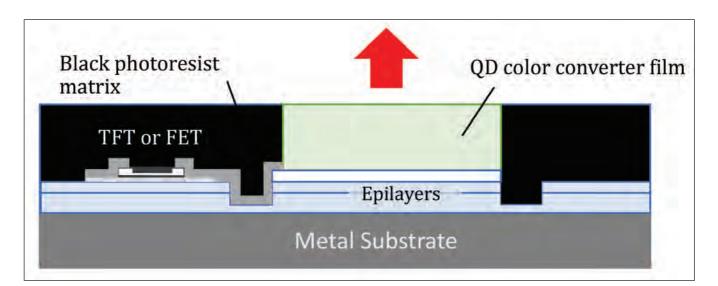

Fabrication of our full-colour, active-matrix display begins by producing a dense array of blue-emitting LEDs monolithically across the surface of the epilayers. Each pixel comprises three sub-pixels, with red and green components formed by coating blueemitting elements with quantum-dot down-converting layers (see Figure 4). They can be added as a photoresist matrix, or with an inkjet printer, depending on the size of the LEDs required.

The next step is to add a thin-film transistor circuit to address each of the sub-pixels. We are able to draw on the existing backplane technology used to make OLED displays, with thin-film materials deposited on the sheet, prior to patterning (see Figure 5).

The total thickness , including that of the metal substrate, can be less than 100  $\mu m.$  To reduce crosstalk, quash stray emission and realise better blacks, the spaces between the LEDs can be filled with a commercially available black polymer matrix.

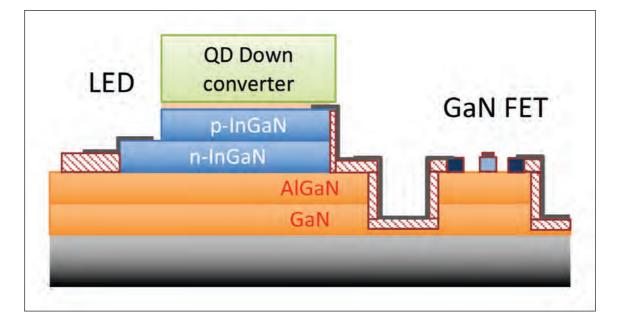

Our technology will continue to advance. In future, we will use the epitaxial GaN sheet that exists on the metal foil to fabricate small, integrated GaN transistors. These devices can be used to control the LEDs (see Figure 6).

By adopting this approach, we are following in the footsteps of the silicon industry. It famously evolved from making circuits by individual wiring of discrete transistors to the high-yield manufacture of highly integrated circuits with billions of transistors on a single chip.

We are confident that over time, the yield and reliability of microLED displays made with our technology will be far higher than those made with chip-transfer methods. However, to begin with, it may be prudent to utilize some redundancy in design, in order to minimize possible LED failure.

Right: Figure 4. The layout of a microLED display made using iBeam technology.

When there is a move to higher-resolution displays, our technology is well-positioned – thanks to the complete area being filled with LED epi, higher resolution displays can be made with smaller additional costs. For our monolithically integrated LED display technology, cost scales with area, rather than the number of pixels. Figure 3. Cost curves of epi-GaN device layers for various deposition methods.

Our approach is not the only one providing monolithic integration. One alternative involves nanowire active regions. However, this relies on conventional rigid substrates, such as silicon and sapphire. Go down that path and the manufacture of large-area displays tends to require the transfer and bonding of LEDs to a backplane.

Figure 5. A sub-pixel cross-section showing a quantumdot, colourconverting film and black photoresist matrix.

#### Colour and gamut

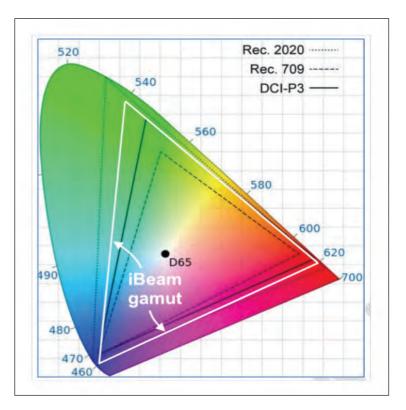

The quantum dot technology that we are advocating to make our displays is advancing, with today's films with a thickness of just a few microns providing nearly full conversion of blue emission to that in the red or green. However, if there are concerns relating to any unwanted blue light that remains in the sub-pixel spectrum, it can be removed with a filter or blue reflector. Makers of displays can choose the quantum dot films to hit specific colour points. The narrow emission of the LEDs and the quantum dots – they have spectral widths of typically 20 nm and 30 nm to 40 nm, respectively – enables saturated colours, along with colour gamuts that are wider than those of conventional LCDs and OLEDs (see Figure 7 for further details).

As the microLED market expands, there is a need for a roll-out of significant additional LED manufacturing capacity in order to make all the required displays. By 2026, some forecasts show 15 percent of the 2 billion cellphone market will feature a 4K microLED display. This alone will require 12 million wafer starts per year, a figure comparable to the total for all LEDs that will be manufactured in 2019. Factor in wearables, TVs, and other display formats, and manufacturing volumes are set to be far higher than this figure.

Our low-cost, roll-to-roll capability can make this ramp possible. Just one wide-web, roll-to-roll production facility could equal today's total worldwide LED epi production.

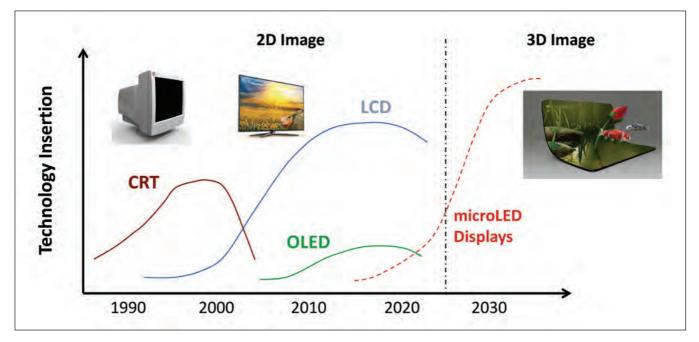

Beyond 2025, displays based on two-dimensional flat screens are expected to be superseded by those that create images in a three-dimensional space (see Figure 8). This can be accomplished by placing an array of emitters, such as microLEDs, over a microlens array. However, to ensure that the light-field display has a high resolution, in addition to compression of huge amounts of data, it must feature billions of pixels with a pitch that could be as small as 5  $\mu$ m.

Figure 6. The sub-pixel LED can be integrated with an GaN/AIGaN FET transistor device, by integrating the FET in the epi structure.

Such a colossal number of pixels is impractical for mass transfer approaches, but can be realised with our monolithic integration technology.

In short, a promising future lies ahead for our technology, which enables the manufacture and integration of microLEDs on large area, metal foils. Wearables, augmented reality, mobile products and even large displays will benefit, due to the many great attributes of our technology. They include: a flexible, light-weight substrate that enables displays to fit curved surfaces and ease of integration into products; the use of direct-emitting LEDs, which allow outdoor viewing and produce a high dynamic range, a wide colour gamut and deep blacks; low cost, due to monolithic integration and compatibility with highvolume roll-to-roll manufacturing techniques; and the promise for light-field displays, the three-dimensional displays of the future.

Further reading

United States Patent 9,735,318 B, V. Matias and C. Yung.

V. Matias, Photonics West Presentation, 2018

Yole Développement, "Are MicroLEDs a credible alternative to LCD and OLED?" SID Display week business conference, (2018)

G-S. Chen *et al*. IEEE Phot. Tech. Lett. **30** 262 (2018)

Figure 7. Three popular gamut standards are targets for new products. Rec. 709, also called sRGB, is the current HDTV standard. However, products such as the Apple iPhone and Samsung Galaxy have already moved to embrace DCI-P3, the digital cinema standard, and future products are targeting the most difficult laser-based Rec. 2020 standard. iBeam technology will be capable of exceeding DCI-P3 and nearly meeting that of Rec. 2020 without requiring lasers.

Figure 8. Historical evolution of displays and expectations into the future.

#### **CONFERENCE 26-27 MARCH 2019** Sheraton Airport Hotel Brussels

Connecting, informing and inspiring the compound semiconductor industry

## CS INTERNATIONAL 2019 CONFERENCE SPEAKERS ANNOUNCED!

With over 40 presentations and a record breaking number of sponsors, the ninth CS International is set to be the biggest and best yet!

## **Book your place NOW!**

www.cs-international.net/register to secure your place It's set to be another sellout

To be held again at the Sheraton Airport Hotel in Brussels on 26 - 27 March 2019, CS International will once more prove to be the must-attend event for the global compound semiconductor community.

Delivering over 40 talks CS International will provide comprehensive coverage of the global semiconductor industry exploring 5 key themes

- Propelling the power electronics revolution

- Pushing the performance envelope

- Speeding communication

- Opportunities for LEDs and lasers

- Targeting Transportation

Each theme includes talks given by the leading decision makers and influencers within the industry.

## This two day event

#### Covers FIVE Themes (Speakers announced to date)

#### PROPELLING THE POWER ELECTRONICS REVOLUTION Sponsored by ClassOn How can the manufacture of SiC devices evolve, so that they capture a greater share TECHNOLOGY of the power electronics market? And what are the opportunities for the GaN-on-silicon HEMT? **SPEAKERS** • Farid Medjoub – IEMN Increasing the blocking voltage of GaN HEMTs - KEYNOTE O Richard Eden – IHS Markit Is the infrastructure in place to ramp SiC and GaN production? - ANALYST • Ralf Lerner – X Fab Printing GaN HEMTs onto silicon CMOS O Cem Basceri – Qromis 200mm GaN Power: Technology and Commercialization Status on QST Platform O Mohammed Alomari – IMS Chips Enabling GaN/Si in an Industry 4.0 environment O Torsten Stoll – Nanometrics Process control solutions for maximum yield in HVM for SiC and GaN power devices O Thomas Uhrmann – EV Group Direct wafer bonding for GaN devices • Ke Xu – Suzhou Nanowin Science & Technology Bulk GaN substrate growth by HVPE technology for GaN-on-GaN devices O Rob Rhoades – Revasum Presentation Title TBC O Julie Orlando – Nanotronics Presentation Title TBC

#### **OPPORTUNITIES FOR LEDS AND LASERS**

Can the MicroLED make an impact? And what are the emerging markets for visible lasers

INSPECTROLOGY

#### **SPEAKERS**

- Masahiro Murayama Sony [KEYNOTE] Watt-class blue and green lasers

Pars Mukish - Yole Développement - [ANALYST] 3D Imaging/Sensing: The next killer application for laser diodes?

Hiromi Fujita - Asahi Kasei Antimonide LEDs for gas sensing

Mark McKee - Veeco

- Accelerating Photonics growth through advances in High Performance As/P MOCVD and Wet Processing technology • Liyang Zhang - Enkris Semiconductor

- Mastering the manufacture of microLEDs on silicon • Norbert Lichtenstein - II-VI Incorporated

- The tremendous opportunities for the VCSEL **• Babu Dayal Padullaparthi - Sanan IC**

- Semiconductor lasers and detectors for DCI, 5G Front-haul, 3D Sensing & beyond

- Joe Wu Sino Nitride Semiconductor The fabrication of high quality low cost free-standing GaN substrates and GaN templates

Sponsored by

#### SPEEDING COMMUNICATION

Are faster lasers going to lead us into a new era of communication? Or will it be the build out of 5G?

#### **SPEAKERS**

- Roger Hall Qorvo [KEYNOTE] Pushing Performance in RF for 5G Networks

- Eric Higham Strategy Analytics [ANALYST] More data: More wireless or more fibre

- Valery Tolstikhin Intengent Fabless PICs in InP: Why, What, and How?

- David Danzilio WIN Semiconductors GaN-on-SiC Technologies for 5G Radio Access

- Edward Wasige EU Project-IBROW Project Mm-wave/THz Multi-Gigabit Wireless Links – the iBROW Project

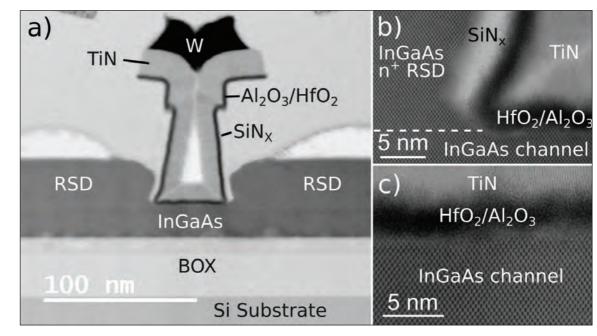

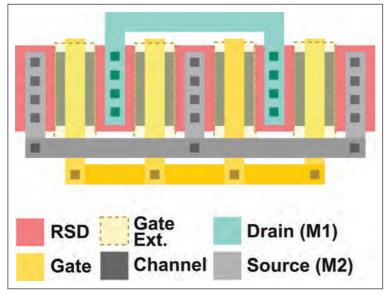

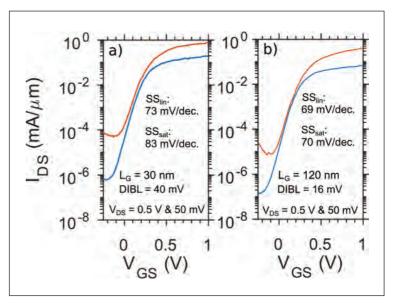

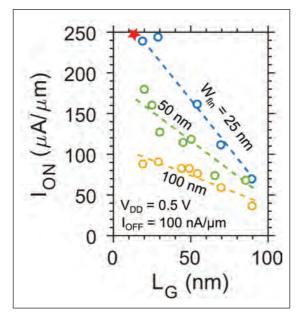

- Gong Xiao National University of Singapore/MIT Alliance Targeting mm-wave communications with wafer-level integration of InGaAs HEMTs and silicon CMOS

Mikko Soderlund – Beneg

- ALD for Compound Semi Power and RF industrial applications

PUSHING THE PERFORMANCE ENVELOPE Sponsored by PFL Where will heterogeneous integration take us? And how can we extract the ultimate performance out of wide bandgap semiconductors? **SPEAKERS** O Bernardette Kunert – imec III/V Nano-ridge Engineering for novel Device Integration on Si [KEYNOTE] O Remy Comyn – Knowmade Innovators in Power SiC - [ANALYST] O Gabriele Formicone – Integra Increasing the Power of Solid-State RF Amplifiers O Marco Malinverni – Exalos Superior superluminescent LEDs O Markus Behet – EpiGaN GaN on Si - A Key enabling technology for 5G O Andy Sellars – Compound Semiconductor Applications CATAPULT Accelerating the commercial application of compound semiconductors O Gerald Klug – DISCO HI-TEC EUROPE Laser-lift-off (LLO) and CONDOx for wafer ultra-thinning process f or 3D stacked devices, TSV, eWLB and WLCSP wafers O David Lishan – Plasma-Therm Extending performance in advanced packaging with low temperature, low damage plasma technologies O Jens Voigt – AIXTRON Enabling Global Mega Trends with Compound Semiconductors O John Ghekiere – ClassOne Advancing Performance of Compound Semiconductor Devices Through Advanced Plating Processes O Mukundkrishna Raghunathan – KLA Corporation Presentation Title TBC

#### TARGETING TRANSPORTATION

Can the strengths of SiC drive its adoption in electric vehicles? And what are the opportunities for III-V optoelectronics in the cars of today and tomorrow?

#### **SPEAKERS**

- Aly Mashaly Rohm Semiconductor [KEYNOTE] Giving Formula E racing cars an edge

- Hong Lin Yole Développement [ANALYST] SiC and GaN adoption by EV/HEV market

All speakers and presentations are subject to change. ©2019 Angel Business Communications Ltd.

PLATINUM SPONSORS

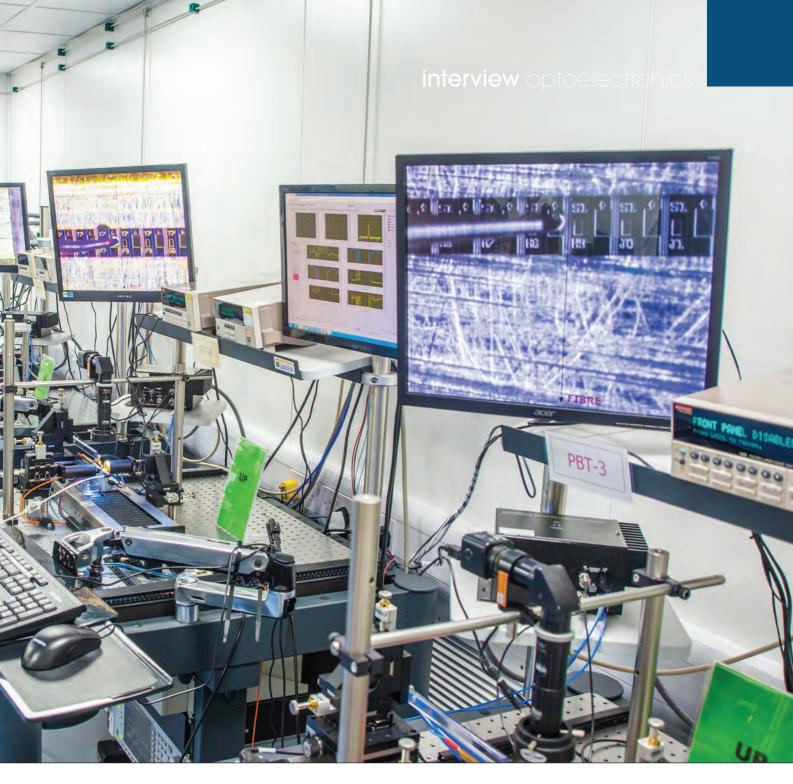

SUPPORTED EPIC EVALUATION CONSISTENT interview optoelectronics

## Full steam ahead for CST Global

While Brexit is doing no favours to CST Global, it is certainly not derailing its phenomenal growth, foundry build-out and expansion of its customer base. Company CEO Neil Martin discusses all this and more in an interview with Richard Stevenson.

#### $\checkmark$ Has 2018 been the best year ever for CST Global?

A I think it was our best ever year. We grew, and there was also an unseen side, namely contractual commitments. In addition to our current customer base, last year saw the level and quality of customer interest in potential contracts increase substantially. We've done a huge amount of product and process development on behalf of those new contracts, and we expect orders to follow this year.

#### Why are sales ramping up so fast?

Basically, III-V technology is really starting to emerge in multiple sectors, in multiple markets.

So we are growing significantly across the board.

One of the major drivers is the movement of data. The communications business is driven along fibre, and the only way to do that is with ever-increasing quantities and capabilities of laser chips. And that's all III-Vs. When you look at the massive investments - whether it's faster and faster corporate, or a hybrid between photonic and corporate data centres - the next-generation stuff for super data centres is going to be pretty much 90 percent fibreorientated. That flows back into the component requirements for these massive data centres.

Then look at sensing, for remote and autonomous vehicles. That's always going to

be hybrid technologies, using lasers with specific wavelengths, because that means that you can detect specific things. We are seeing a lot of development and product enhancement going on, and that will continue. There's not going to be one absolute, single system that does it all.

Then, if you look at handhelds, there is huge amount of environmental concern, in Asia particularly, in relation to air quality. And there's facial recognition. That's all III-V driven.

#### Q How close are you to full capacity?

А

We are adding capacity all the time. Like any production facility, there are always parts under pressure. By March we will have a duplicate production line and the facility will ave expanded significantly. Then it's just question of scaling that.

By the end of this calendar year we will be very much pressing up against the walls. So clearly some significant thoughts about further investment are required in 2019.

#### What are you doing to expand your capacity in the fab?

We are bringing in more automated toolsets. Fabs for III-Vs tend to have islands of pieces of equipment. We are just starting to link them together with tracks and various other things. We are looking at multi-load systems, so that we can condense processes and reduce the

Testing bars with a tool that can 'pick and place' is helping to increase throughput at CST Global.

#### interview optoelectronics

handling. There is a lot of capacity on the footprint that can be gained by developing machinery and key processes, before you have to go elsewhere.

The second line gives us a lot of risk management advantage, which is significant for some larger customers. At the same time it is clearly increasing capacity, by adding better, more modern equipment.

#### Are you on a recruitment drive?

Yes, always. Good people are hard to get, so we are always looking across the board. There's always room for laser design experience, and some excellence in process development engineering. These are occasional specialisms that we have to look at. We recruited quite well on the materials front last year, but that's another area that we'll need to continue to work on.

We've also put a lot of effort into developing our own skills pipeline. We have people on placement that still have got three years of academia to go through before they become available to us.

CST clearly benefits from a nationally diverse workforce. This appears to be at odds with the message from the UK Government, which is one of strengthening its boarders, and making it harder for companies to recruit those from overseas. Are you concerned? Big time. We have got something like 17 or 18 PhDs, and only four of them are UK nationals. We have a very simple philosophy, which has been borne out to be true – the main reason that personnel leave companies is because they feel unwanted and not looked after. If you feel unwanted, you automatically – even maybe subliminally – start to turn off. That is completely lost on a certain section of the political establishment.

You are involved in lots of collaborative projects that involve countries that are in the European Union. It's hard to say, but what will be the impact of Brexit on this?

We had a very high success rate of getting through the key projects over the years, and that's already slumped dramatically. We're not invited to the party. And we always were. So there's no question that that's impacting us.

Do these projects take up a substantial proportion of foundry time?

No. We allocate a level of capacity. It's mainly the time and expertise of some key individuals. We support that activity, obviously, but we are mainly doing commercial work.

On the one hand, we get to develop of our own skillset, increase our knowledge base through those programmes, and have the opportunity to try to future-proof the market for our company. But we are interfacing with

The foundry at CST Global includes an automatic bar stacker.

#### Opportunities for optoelectronic devices in quantum technologies

One promising, emerging class of applications for III-Vs is that described as quantum technologies. This rather vague moniker refers to applications exploiting quantum interference, entanglement and tunnelling. It is these quantum phenomena that lie at the heart of atomic clocks, gravity sensors, quantum computers and quantum communications; and rely on laser cooling technology, which can be accomplished with laser diodes based on GaAs, GaN and InP.

The opportunities for quantum technologies were discussed and debated by engineers, academics, politicians, and representatives of funding agencies, at a one-day meeting held at the House for an Art Lover, Glasgow, in mid-November.

At this gathering, organised by CST Global, Sir Peter Knight from Imperial College London delivered a key note presentation entitled *Quantum Technologies for a Networked World*.

Knight began by highlighting the high level of investment in quantum technologies by the UK – it has allocated £400 million to a national programme. Some of those working in the UK will have also been able to draw on the € billion Quantum Technology Flagship, a European initiative. While these level of funding are impressive, they appear to be dwarfed by the US and China, which may be injecting as much as \$2.4 billion and \$10 billion, respectively.

The UK investment in quantum technology that began in 2014 is already paying dividends. It has driven the launch of the first 16 start-ups that are exploiting quantum technology; it has generated £30 million of investment; and it has created more than a hundred jobs.

Knight explained that the motivation behind such high levels of investment in the UK is in part due to improving the stability of financial markets, so that there is not a recurrence of the 'flash crash' – a trillion dollar crash in May, 2010, that lasted for just over half an hour. High frequency trading can contribute to panic on the markets, while the widespread deployment of atomic clocks would lead synchronisation at every node – that is, every switch, router, server, processor and GPS receiver – and ultimately greater resilience on stock exchanges.

Atomic clocks are not a new technology. This form of clock, which has a timing mechanism based on the superposition of quantum states, dates back to the 1950s. Initially, these clocks needed to operate in the lab, but applications in defence and communications have driven miniaturisation. Scaling has been spearheaded by the hugely ambitious chip-scale atomic clock programme that ran from 2002 until 2008. This effort failed to fulfill very demanding targets, but did lead to the development of a 17 cm<sup>3</sup> chip-based clock by Symmetricom that drew less than 120 mW. Knight explained that efforts to improve on this include a design pioneered in the UK by Starthclyde and Imperial College, involving a microfabricated grating to aid laser cooling.

Another market with tremendous potential is that of quantum sensors. According to Knight, this sector includes quantum chips for accelerometry, gyroscopes, gravimetry and magnetometry, and gravity sensors for oil, gas, minerals and defence.